HC-90/95の専用オプションの話

2022.06.05

VHDとかNAPLPSとか色々見えてきた

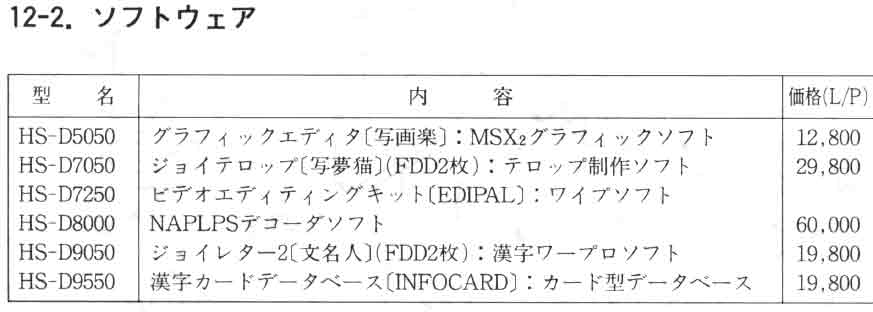

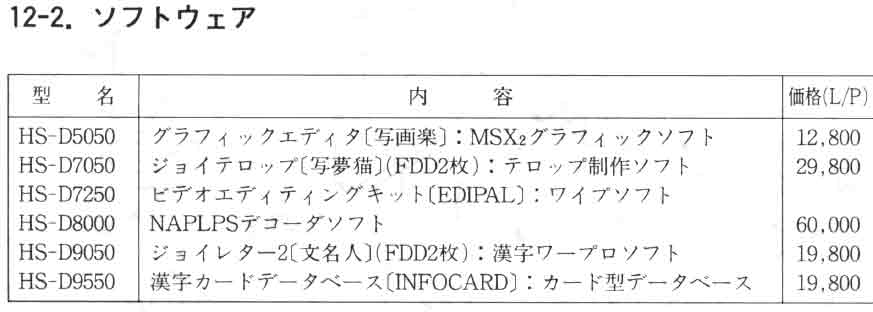

まずオプションとして発売されていたもの

ハードウェアの抜粋

NAPLPSボードは単体売りは無いみたいなので、やはりソフト同梱かなと。

ちゃんとIF-C9CもC9Dも両方載っていて何が違うのかというと、

IF-C9Cはインターラクティブ機能可

IF-C9Dはタッチパネル用RS-232C I/F付

となっている。

じゃあこのインターラクティブ機能ってなんなのよっていうと、

サンダーストームのVHDに

INTERACTIVE DISCって書いてるので、やっぱりゲームとかするにはIF-C9Cが必要。

どう考えてもRS-232CのレベルシフタよりDIL周辺のほうが高そうだけど、IF-C9Dのほうが値段高いらしい。

というわけで、じゃあIF-C9Dは何に使うのよっていう話になるけど、どうもそれ自体の調べはつかなかったものの、さらにその後継システムと思われるものが情報として残ってた。

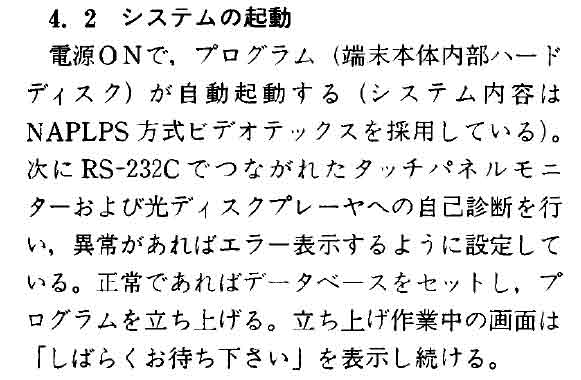

情報管理っていう雑誌(?)の1992.02号に「東京都葛西臨海水族園の情報検索システム」ってのがあって、

というこれを見ただけでもなかなかにぶっ飛んでる図があった。

HC-90にLANって何・・・。

あと、明確には書かれていないけど、NAPLPS通信にもRS-232C使うから、NPLPS通信用のRS-232C端子と、RS-DV(RS-divider?)を経由してタッチパネルとか光ディスクプレーヤーを制御するためのRS-232Cの2系統が必要になる。

さらにツッコミどころはあって、

ハードディスク内蔵って何・・・・・・

ブロック図に書かれてるTQ-3200Fは動画対応光ディスクプレーヤーですが、さらっと先ほど書きましたが1992年の資料です。ビデオCDの規格ができたのが1993年です。

この文献に書かれてますが、レコーダはTQ-3100Fというものを使うようです。追記型らしいのでCD-RをベースにしたLDでしょうか。これもNational technical reportという雑誌(?)に詳細載っているようなので、国会図書館とかに問い合わせれば資料手に入るかも?

まあ、ここはMSXに直接関係ないのでそういうものなんだろうということにしておきます。

ここまでくるとそもそもこの文献のHC-90って想像してるものと別物なんじゃねーのって気がしますが、きちんと「ビクター製MSX2」って書いてあります。

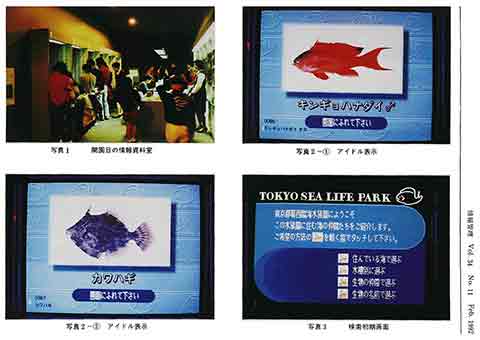

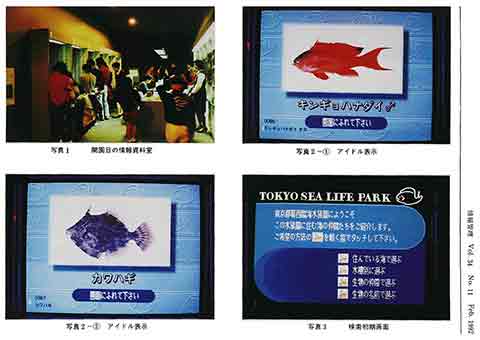

動いてる様子はこんな感じらしいです。

たしかになんとなくMSXっぽい雰囲気はありますね。

で、ここまでVHDが一切出てこなかったですが、光ディスクプレーヤーがVHDに置き換わったとすると、VHD I/F(Dsub15)でVHDを制御して、VHD I/FのRS-232Cでタッチパネル制御、本体RS-232Cは何か別用途(ホストと通信とか)、必要であればNAPLPSも導入、というシステムが構築できるのは間違いないでしょう。

なので、こういったかなり特定用途向けのI/Fであろうことが想像できます。

まずオプションとして発売されていたもの

ハードウェアの抜粋

NAPLPSボードは単体売りは無いみたいなので、やはりソフト同梱かなと。

ちゃんとIF-C9CもC9Dも両方載っていて何が違うのかというと、

IF-C9Cはインターラクティブ機能可

IF-C9Dはタッチパネル用RS-232C I/F付

となっている。

じゃあこのインターラクティブ機能ってなんなのよっていうと、

サンダーストームのVHDに

INTERACTIVE DISCって書いてるので、やっぱりゲームとかするにはIF-C9Cが必要。

どう考えてもRS-232CのレベルシフタよりDIL周辺のほうが高そうだけど、IF-C9Dのほうが値段高いらしい。

というわけで、じゃあIF-C9Dは何に使うのよっていう話になるけど、どうもそれ自体の調べはつかなかったものの、さらにその後継システムと思われるものが情報として残ってた。

情報管理っていう雑誌(?)の1992.02号に「東京都葛西臨海水族園の情報検索システム」ってのがあって、

というこれを見ただけでもなかなかにぶっ飛んでる図があった。

HC-90にLANって何・・・。

あと、明確には書かれていないけど、NAPLPS通信にもRS-232C使うから、NPLPS通信用のRS-232C端子と、RS-DV(RS-divider?)を経由してタッチパネルとか光ディスクプレーヤーを制御するためのRS-232Cの2系統が必要になる。

さらにツッコミどころはあって、

ハードディスク内蔵って何・・・・・・

ブロック図に書かれてるTQ-3200Fは動画対応光ディスクプレーヤーですが、さらっと先ほど書きましたが1992年の資料です。ビデオCDの規格ができたのが1993年です。

この文献に書かれてますが、レコーダはTQ-3100Fというものを使うようです。追記型らしいのでCD-RをベースにしたLDでしょうか。これもNational technical reportという雑誌(?)に詳細載っているようなので、国会図書館とかに問い合わせれば資料手に入るかも?

まあ、ここはMSXに直接関係ないのでそういうものなんだろうということにしておきます。

ここまでくるとそもそもこの文献のHC-90って想像してるものと別物なんじゃねーのって気がしますが、きちんと「ビクター製MSX2」って書いてあります。

動いてる様子はこんな感じらしいです。

たしかになんとなくMSXっぽい雰囲気はありますね。

で、ここまでVHDが一切出てこなかったですが、光ディスクプレーヤーがVHDに置き換わったとすると、VHD I/F(Dsub15)でVHDを制御して、VHD I/FのRS-232Cでタッチパネル制御、本体RS-232Cは何か別用途(ホストと通信とか)、必要であればNAPLPSも導入、というシステムが構築できるのは間違いないでしょう。

なので、こういったかなり特定用途向けのI/Fであろうことが想像できます。

続・IF-C9D

2022.05.31

落札した人と思われる人の投稿がMRCに。

https://msx.org/forum/msx-talk/hardware/vhd-interface-for-victor-hc9095

IF-C9Dは、板自体はC9Cと同じだけどもROMとVCMとPPIしか乗ってなくって、DIL入ってないっぽい。

DIL入ってないってことはCSYNCとかVHD DATAとか受けれないはずだけどどうなんだろう。

少なくともIF-C9Cの上位互換ってことはなく別物っぽい。

とするとROMの中身も別物だろうなー。普通のVHDソフト(VHD BASIC)動くのかな。

https://msx.org/forum/msx-talk/hardware/vhd-interface-for-victor-hc9095

IF-C9Dは、板自体はC9Cと同じだけどもROMとVCMとPPIしか乗ってなくって、DIL入ってないっぽい。

DIL入ってないってことはCSYNCとかVHD DATAとか受けれないはずだけどどうなんだろう。

少なくともIF-C9Cの上位互換ってことはなく別物っぽい。

とするとROMの中身も別物だろうなー。普通のVHDソフト(VHD BASIC)動くのかな。

Z80アクセラレーターボード

2022.05.25

HB-F1XDJをパワーアップしようという妄想です

パナ2+はカスタム(T9769C)で固められててあまりいじれないのですが、SONY機はZ80がそのまま載ってるのでいろいろいじりやすい機体ですね。

今ではZ80Aに比べて高速なFPGAが安価で容易に手に入ります(入荷待ち状態続いてて容易じゃないけどな)。

そこで、Z80を取り払ってそこに付くアクセラレーターボードを作れないかなという妄想です。

まず真っ先に思いつくのがとりあえずクロックアップですが、色々検証した結果XDJのメインボードはクロックアップ耐性が非常に低いということがわかってます(動いても1.5倍速程度)。

というかそもそもクロックアップなんて定格外動作ですし、貴重な(?)マシンにそんなことしたくありません。

なので、手段としては、アクセラレーターボードにDRAMも載せて、FPGA(Z80)とDRAM間のみ高速アクセスさせて、外部(XDJ本体=外部スロットやIO)にはウェイトを入れて正規タイミングで動かしてしまおうとなります。

今のFPGAであれば高速クロックでも容易に動きますし、ALUのバス幅を増やして命令のステート数を削減することも可能です。

こうすることでXDJ側は一切定格外の高速動作などさせる必要なく高速化が可能です。

アクセラレーターボードでDRAMを持ち、かつ、高速アクセスするとなると当然アクセラレーターボード側にスロット選択レジスタを持つ必要があります。

すると付随的にBIOS ROMなども乗っ取りが可能になりますので、ROMアクセスも高速化することができます。

そもそもBIOS ROMをDRAMにコピーして動かせば、DRAMのページモードアクセスの恩恵でさらに高速化することができます。だいたいZ80@3.58MHz比で12倍速くらいで動かせますね。

という、なんかどこかで聞いたことあるような仕様になりますね。ええ、妄想ですが。

ところで、turboRのプライマリーマッパーを4MByteにすると微妙な不具合が色々あります。

・DOS2カーネルがプライマリー4MByteにするとDRAMモードセグメント確保処理にバグがあって起動しない

・そもそもDOS2のマッパーサポートルーチンの仕様が1SLOTあたり255セグメント(256ではない)しか扱えないので、DRAMモード使用セグメントと不整合する

ちなみにこれはプライマリー以外でもそうなので、4MByteマッパーは最後の1セグメント使われません

・MSX-Viewが1MByteまでしか動かない(なんとパナマッパーのDRAMマッピング機能を使っている)

当事は4MByteとか検証すらされてなかったんでしょうね。

後日追記:2022/07/31

もう少し詳しい詳細はこちら

http://d4.princess.ne.jp/msx/other/xdjodp/

パナ2+はカスタム(T9769C)で固められててあまりいじれないのですが、SONY機はZ80がそのまま載ってるのでいろいろいじりやすい機体ですね。

今ではZ80Aに比べて高速なFPGAが安価で容易に手に入ります(入荷待ち状態続いてて容易じゃないけどな)。

そこで、Z80を取り払ってそこに付くアクセラレーターボードを作れないかなという妄想です。

まず真っ先に思いつくのがとりあえずクロックアップですが、色々検証した結果XDJのメインボードはクロックアップ耐性が非常に低いということがわかってます(動いても1.5倍速程度)。

というかそもそもクロックアップなんて定格外動作ですし、貴重な(?)マシンにそんなことしたくありません。

なので、手段としては、アクセラレーターボードにDRAMも載せて、FPGA(Z80)とDRAM間のみ高速アクセスさせて、外部(XDJ本体=外部スロットやIO)にはウェイトを入れて正規タイミングで動かしてしまおうとなります。

今のFPGAであれば高速クロックでも容易に動きますし、ALUのバス幅を増やして命令のステート数を削減することも可能です。

こうすることでXDJ側は一切定格外の高速動作などさせる必要なく高速化が可能です。

アクセラレーターボードでDRAMを持ち、かつ、高速アクセスするとなると当然アクセラレーターボード側にスロット選択レジスタを持つ必要があります。

すると付随的にBIOS ROMなども乗っ取りが可能になりますので、ROMアクセスも高速化することができます。

そもそもBIOS ROMをDRAMにコピーして動かせば、DRAMのページモードアクセスの恩恵でさらに高速化することができます。だいたいZ80@3.58MHz比で12倍速くらいで動かせますね。

という、なんかどこかで聞いたことあるような仕様になりますね。ええ、妄想ですが。

ところで、turboRのプライマリーマッパーを4MByteにすると微妙な不具合が色々あります。

・DOS2カーネルがプライマリー4MByteにするとDRAMモードセグメント確保処理にバグがあって起動しない

・そもそもDOS2のマッパーサポートルーチンの仕様が1SLOTあたり255セグメント(256ではない)しか扱えないので、DRAMモード使用セグメントと不整合する

ちなみにこれはプライマリー以外でもそうなので、4MByteマッパーは最後の1セグメント使われません

・MSX-Viewが1MByteまでしか動かない(なんとパナマッパーのDRAMマッピング機能を使っている)

当事は4MByteとか検証すらされてなかったんでしょうね。

後日追記:2022/07/31

もう少し詳しい詳細はこちら

http://d4.princess.ne.jp/msx/other/xdjodp/

2022.06.05 01:18

|

2022.06.05 01:18

|