FS-A1STの設計不良

2023.02.01

A1STのハードウェア設計にバグを見つけてしまいました。

IOリード機能を持つカートリッジを使用した場合、Z80モードだとバス競合が起きて漢字フォントが化けたり、最悪故障する可能性があったり(!)というネタです。

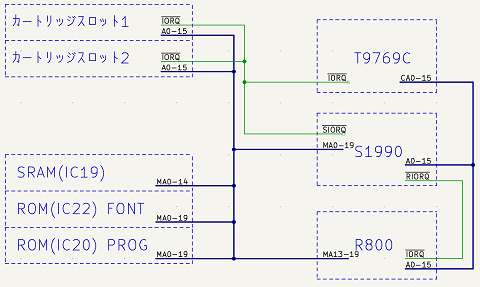

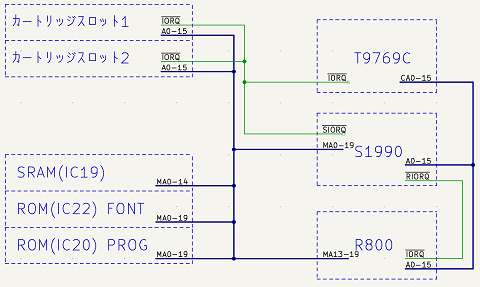

まずturboRのアドレスバスと/IORQ周りですが、こんな感じになっています。

ROMの容量とかはGT基準になっていますが、CSの使い方(S1990が出す)が違うくらいで基本的にはSTも同じ構成です。

着目すべきところは、

・漢字ROMもプログラムも同じROMに突っ込んである

・カートリッジスロットに接続されているアドレスバスは、それらのROMと同じである

というところです。

まずカートリッジスロット基準での漢字ROMのIOリードのバスサイクルを考えると、A0-7には漢字ROMリードのアドレス(第1水準なら0D9h)が出てきて、/IORQ=L、/RD=Lとなるはずです。

なので、この構成上、漢字ROMを読み込むときはIC22の下位アドレスは0D9h固定になるべきで、MAは8-19しか自由に使えないことになります。

かなりトリッキーなROMマッピングをすればそれでもギリギリ回避できそうにも思いますが、実際にはそんな挙動をしているわけではなく、普通に連続アドレスに漢字フォントは格納されています。

※ちなみにIOアクセス時のA8-A15はZ80の隠れ動作として、CもしくはAレジスタが出力されるので、互換性を考えると上位bitも自由に使えません。

というわけで、実際に漢字ROMをIOリードする場合、MAにはIC22の漢字フォントが格納されているアドレスが出力されます(S1990が出力する)。

もちろん、カートリッジバスからもそのアドレスが見えます。

では次に/IOQRの動作ですが、こちらZ80モードの場合、T9769C(=Z80)の/IORQがそのままカートリッジスロットに出力されます(注:後述あり)。

なので、/IORQ=L、かつ、アドレスは嘘、という状態になります。/RD=Lも出力されます。

つまり、アドレス0D9hを読み込んだにもかかわらず、カートリッジスロットにはまったく別のアドレスのIOリードリクエストが発行されることになります。ですので、IOリード機能を持つカートリッジが繋がっていると、場合によってはバス競合が発生してデータ化けなどが起きます(実機確認済み。カートリッジ側の駆動能力によっては起きない)。

どのアドレスが競合するかは、読み出す漢字(FONTのアドレス)によります。実質的には一文字分のアクセスで32byte読み出すので、32回異なるアドレスをROMから読み出すため、連続32アドレスのどこかに被れば競合しますし、文字によりアドレスの上位bitも異なりますので、高確率で競合します。

ではなぜSTだけで起きて、GTでは起きないかという話ですが、先に書いた「注:後述あり」の個所になります。

GTの場合はT9769C→カートリッジの/IORQの間にマスク回路が入っており、0D8h~0DFhはカートリッジスロットには/IORQを発行しないように修正が入っています。

つまり、GT設計時点ではPanasonicはこの問題を認識しており、対処したということになります。バス競合により故障の原因と成り得ますがSTはリコール等はされていないと記憶しています。

なので、GTは外付け漢字ROMが使用できません。

というか、STはほとんど使ったことがなかったので、ごく近年までturboRは外付け漢字が使えないものだと思っておりましたが、実は外付け漢字ROMが使えないのはGTだけだったようです。

あー、ちなみにMSXとは全く関係ない別件ですが、Panasonicは設計不良が原因の故障であってもよほどクリティカルなものでない限りそれを認めないみたいですよ。保証期間過ぎたあとであればたとえ設計不良であっても有償修理と言われます(実績あり)。

IOリード機能を持つカートリッジを使用した場合、Z80モードだとバス競合が起きて漢字フォントが化けたり、最悪故障する可能性があったり(!)というネタです。

まずturboRのアドレスバスと/IORQ周りですが、こんな感じになっています。

ROMの容量とかはGT基準になっていますが、CSの使い方(S1990が出す)が違うくらいで基本的にはSTも同じ構成です。

着目すべきところは、

・漢字ROMもプログラムも同じROMに突っ込んである

・カートリッジスロットに接続されているアドレスバスは、それらのROMと同じである

というところです。

まずカートリッジスロット基準での漢字ROMのIOリードのバスサイクルを考えると、A0-7には漢字ROMリードのアドレス(第1水準なら0D9h)が出てきて、/IORQ=L、/RD=Lとなるはずです。

なので、この構成上、漢字ROMを読み込むときはIC22の下位アドレスは0D9h固定になるべきで、MAは8-19しか自由に使えないことになります。

かなりトリッキーなROMマッピングをすればそれでもギリギリ回避できそうにも思いますが、実際にはそんな挙動をしているわけではなく、普通に連続アドレスに漢字フォントは格納されています。

※ちなみにIOアクセス時のA8-A15はZ80の隠れ動作として、CもしくはAレジスタが出力されるので、互換性を考えると上位bitも自由に使えません。

というわけで、実際に漢字ROMをIOリードする場合、MAにはIC22の漢字フォントが格納されているアドレスが出力されます(S1990が出力する)。

もちろん、カートリッジバスからもそのアドレスが見えます。

では次に/IOQRの動作ですが、こちらZ80モードの場合、T9769C(=Z80)の/IORQがそのままカートリッジスロットに出力されます(注:後述あり)。

なので、/IORQ=L、かつ、アドレスは嘘、という状態になります。/RD=Lも出力されます。

つまり、アドレス0D9hを読み込んだにもかかわらず、カートリッジスロットにはまったく別のアドレスのIOリードリクエストが発行されることになります。ですので、IOリード機能を持つカートリッジが繋がっていると、場合によってはバス競合が発生してデータ化けなどが起きます(実機確認済み。カートリッジ側の駆動能力によっては起きない)。

どのアドレスが競合するかは、読み出す漢字(FONTのアドレス)によります。実質的には一文字分のアクセスで32byte読み出すので、32回異なるアドレスをROMから読み出すため、連続32アドレスのどこかに被れば競合しますし、文字によりアドレスの上位bitも異なりますので、高確率で競合します。

ではなぜSTだけで起きて、GTでは起きないかという話ですが、先に書いた「注:後述あり」の個所になります。

GTの場合はT9769C→カートリッジの/IORQの間にマスク回路が入っており、0D8h~0DFhはカートリッジスロットには/IORQを発行しないように修正が入っています。

つまり、GT設計時点ではPanasonicはこの問題を認識しており、対処したということになります。バス競合により故障の原因と成り得ますがSTはリコール等はされていないと記憶しています。

なので、GTは外付け漢字ROMが使用できません。

というか、STはほとんど使ったことがなかったので、ごく近年までturboRは外付け漢字が使えないものだと思っておりましたが、実は外付け漢字ROMが使えないのはGTだけだったようです。

あー、ちなみにMSXとは全く関係ない別件ですが、Panasonicは設計不良が原因の故障であってもよほどクリティカルなものでない限りそれを認めないみたいですよ。保証期間過ぎたあとであればたとえ設計不良であっても有償修理と言われます(実績あり)。

MSX実機で高音質再生したい

2022.11.12

MSX実機の音なんて所詮ノイズまみれで・・・

と思っていましたが、にがさんが頑張ってくれてかなり高音質な音源カートリッジを作成されています。

f特が変わって高音が潰れなくなるだけとか、DSPでごまかすとかそういう話ではなく、できる限り低ノイズな加工されていない音が出ているかなと。

といわけで、

・似非SCCDisk(試作品)

実SCCチップ(2212P003)を流用して、できるだけ高音質化したものです。ついでにSCC付き似非Ramとして使えます。

そのうち作成キットが発売されるらしい?

・SoundeCoreSLOT EX(試作品)

PSG+OPLL搭載の拡張スロットです。拡張スロットの使い勝手は形の都合で微妙。

MI68で販売されました(過去形)

再販はありそうです。

・OPNA Sound Cartridge(試作品)

YM2608が載ってます。個人的にはMSXにOPNA載せても過去資産が使えるわけでもないしなあ、とも思ってます。

近々発売されるらしいです。

どれも過去MSX用の他の音源カートリッジと比べても高音質と思います。

Chiptune界隈で実機からの生録にこだわりがある人とかにはとてもよさそうです。

ぜひ良い環境で聞いてみてください。

と思っていましたが、にがさんが頑張ってくれてかなり高音質な音源カートリッジを作成されています。

f特が変わって高音が潰れなくなるだけとか、DSPでごまかすとかそういう話ではなく、できる限り低ノイズな加工されていない音が出ているかなと。

といわけで、

・似非SCCDisk(試作品)

実SCCチップ(2212P003)を流用して、できるだけ高音質化したものです。ついでにSCC付き似非Ramとして使えます。

そのうち作成キットが発売されるらしい?

・SoundeCoreSLOT EX(試作品)

PSG+OPLL搭載の拡張スロットです。拡張スロットの使い勝手は形の都合で微妙。

MI68で販売されました(過去形)

再販はありそうです。

・OPNA Sound Cartridge(試作品)

YM2608が載ってます。個人的にはMSXにOPNA載せても過去資産が使えるわけでもないしなあ、とも思ってます。

近々発売されるらしいです。

どれも過去MSX用の他の音源カートリッジと比べても高音質と思います。

Chiptune界隈で実機からの生録にこだわりがある人とかにはとてもよさそうです。

ぜひ良い環境で聞いてみてください。

2023.02.01 23:45

|

2023.02.01 23:45

|