MSX turboRバージョンアップボード

blogのほうに先出しでちょっと書いた奴で、SONY製turboRの夢を見たいという話です。

今ではZ80Aに比べて高速なFPGAが個人でも安価で購入できます。

そこで、Z80を取り払ってそこに付くアクセラレーターボードを作れないかなという妄想です。

●実働デモ

●作成した物

こちらが作成したものの現物となります。

色々試作段階で試行錯誤してるので、ジャンパー飛び回ってたりしてかっこ悪いですね。

●概要

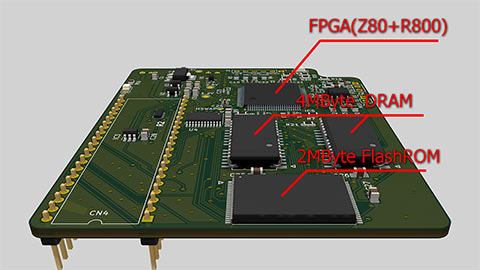

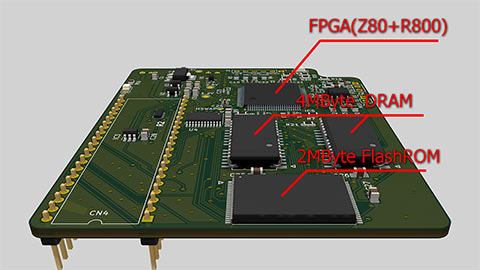

これはつまりどういうものかというと、アクセラレーターボードにFPGA(Xilinx XC3S250E)を載せて、Z80相当コアとR800相当コアを入れます。

また、S1990相当のバスブリッジも作成し、R800時はFPGAとアクセラレータボード上のDRAMは高速アクセスさせて、外部(XDJ本体=外部スロットやIO)にはウェイトを入れて正規タイミングで動かしてしまおうとなります。

アクセラレーターボードでDRAMを持ち、かつ、高速アクセスするとなると当然アクセラレーターボード側にスロット選択レジスタを持つ必要があります。

すると付随的にBIOS ROMなども乗っ取りが可能になりますので、ROMアクセス時には外部(XDJ本体)にメモリアクセスを行わないことで、アクセラレーターボード上にBIOS ROMも載せてBIOS ROMアクセスも高速化することができます。さらにFDC ROMも乗っ取ることでDOS2化も可能です。

※turboRのDOS2はpanasonic系FDCドライバと統合されており、そのままではsony系FDCでは動作できないため、DOS2カーネルにsony系FDCドライバを統合する必要があります。

なので、実質的には物理的な外部スロットアクセス以外のメモリアクセスについては、基本的にアクセラレーターボード上でクローズし、XDJ本体に対してはバスサイクルを発生させません。

カートリッジスロットや拡張スロット選択レジスタ、FDCなどのメモリマップドIOアクセスの必要がある箇所のみ、Z80と同じタイミングでXDJ本体に対してバスサイクルを発生させます。

また、IOポートに関してもZ80と同じタイミングでXDJ本体に対してバスサイクルを発生させます。

この辺りはR800→S1990→MSX-ENGINEとアクセスする際と同じ動作です。

もちろんZ80モード時はそのままバスサイクルを発行しますが、アクセラレーターボード上のDRAMやROMにアクセスする必要がある場合は、バス競合が発生するのでXDJ本体側にはバスサイクルは発行しません。

●メリット

turboR化相当となるメリットは言うまでもないでしょう。

MSX2+の改造というとメモリ増設やクロックアップがわりとよく行われてますが、単体でメモリ増設しても対応しているソフトも極めて少なく、また、クロックアップができてもせいぜい3倍程度でなおかつ使い道もあまりないとなると、改造するリスクに見合うのかというところがあります。

ただ、一気にturboR相当まで改造できるとなるとメリットは多々あるでしょう。また、改造難易度もZ80を取り外してソケットを付けるだけでよく、S1985から信号を引き出すメモリ増設などに比べても難易度は低めです。

また、さらに本物のturboRに対してメリットとなることは

・DRAMを4Mbyte化したことにより、ページサイズが2048byteとなり、ページブレイクの発生頻度が下がる

・FPGAの性能により、追加バスサイクルが発生しない命令はM1ステートのみで実行が終わる(16x16=32bitの掛け算が2clk@7.1MHzで終わる!!)

・DRAMアクセスの最適化によりページブレイクの発生頻度が下がる(ROWアドレスが変わらない限り余分なページブレイクが発生しない)

ということで、R800比で約120%くらいの速度で動くようです。いや、正確にR800の挙動に合わせるの難しかっただけですが・・・。

あとは追加機能として、

・VDPのウェイトがソフトウェアコンフィギュラブル

基本的にはturboR相当の8usウェイトですが、ソフトから変更できます。

※ちなみに8usの根拠はV9958のデータシートなのですが、実際8us空けないとダメな場合は、LMMCで連続でデータを転送する場合のようです。ステータスレジスタきちんと見て転送すれば問題ないですが、Z80だと大抵はソフトでウェイト調整しているので、R800にすると間に合わなくなる可能性があります。

そこを考慮すると(VDPがどのコマンドを実行中でどのレジスタに間接アクセスしていてblanking期間中かどうかでコマンド実行速度がかわるからそこも考慮したりしない限り)一律ウェイト入れるしかなかったのでしょう。

・DRAM容量がソフトウェアコンフィギュラブル

後述しますがメインメモリ4MByteでは動かないソフトがありますので、容量を絞れるようにします。

・スピコン

SONY機のメリットです

このようなボードを作成することで、ほぼturboR相当にバージョンアップすることができました。

また、turboRの隠されている仕様として、スロット#3-3のPanasonicマッパーがあります。このマッパーは通常の内蔵ROMのほか、DRAMを8Kbyte単位でマッピングできたり、バッテリーバックアップ用のSRAMがつながっていたりします。

このマッパーを実装しなくても内蔵ワープロなどが使えないだけと思いがちですが、MSX-Viewはこの機能を使用しているため、MSX-Viewを動作させるのであればこの実装は必須です。せっかくturboR相当になるのにMSX-Viewが動かないのはもったいないので、こちらも実装してあります。

また、バッテリーバックアップSRAMが無いと、内蔵ワープロが使用できません。せっかくなのでこちらも実装します。ただし、バッテリーバックアップ機能は無いため、電源を切ると辞書学習や外字などは削除されます。

あと、せっかくA1GTには12dotフォントという便利なものも内蔵しているので、こちらも移植できるので便利です。

●不具合

ところで、turboRのプライマリーマッパーを4MByteにすると微妙な不具合が色々あります。

・DOS2カーネルがプライマリー4MByteにするとDRAMモードセグメント確保処理にバグがあって起動しない

・そもそもDOS2のマッパーサポートルーチンの仕様が1SLOTあたり255セグメント(256ではない)しか扱えないので、DRAMモード使用セグメントと不整合する

ちなみにこれはプライマリー以外でもそうなので、4MByteマッパーは最後の1セグメント使われません

・MSX-Viewが1MByteまでしか動かない

一部ソフトがメモリ4Mbyteで動かないのはこのあたりのせいです。MSX-Viewはpanasonicマッパーが1MByteしか対応できないので対応が難しいので無視(容量制限モード使用)しますが、DOS2が4MByteで起動しないのはかなり意味がありません。

なので、DOS2へのパッチも必要です。

●リメイク版

そしてこちらが各種修正を反映した量産向けボードの完成イメージになります。

でもXilinxが仕事してくれないのでFPGAが手に入らない!!!\(^o^)/

●追記(2023/4/28)

ありがたいことに興味を持ってくれている人がそれなりに居るようですので、現状についてです。

量産向けボード(のつもり)。

・部品入手

金積めば入手できるようになりました。

ちなみにこのプロジェクトが始動したときはFPGAは2700円で買えました。今8200円くらいします。

その他パーツもかなり値上がりしています。今配布したとしてもA1STが中古で買えるくらいの値段になってしまいます。意味ないですね。

・不具合

いくつか作ってみたところ、個体差(?)で安定しない現象がでています。

解決できないと単体配布ができません(組み込み済みで動作確認した本体ごとならできるかも程度)。

(ゆっくり)調査中ですので、もうしばらくお待ちください。

●追記(2024/1/15)

まずは良い話から。

かなり動作として安定してきて、ベータテスト(人柱)配布を始めました。

MSX VILLAGEさんに紹介記事を書いていただいています。

https://msxvillage.fr/forum/topic-4372-1+upgrade-msx2-vers--turbo-r.php

そして悪い話。

AMD(Xilinx) Spartan3/3A/3AN/3E/3ADSP 製品ファミリの製造中止通知

Spartan3EがEOLった。

どのくらい数でるのかもわからないのに1万円もするチップ数十個とか買えない!

オワタ\(^o^)/

LTBまでに総生産数見込み検討できるだけの一般配布開始できるかなあ・・・。

感想、要望、バグ報告、その他何かありましたら、メールもしくは掲示板にてご連絡ください。

裕之

ホームに戻る